接着上周的内容,首先介绍的只读存储器(ROM)。

ROM

只读存储器(Read-Only Memory),顾名思义,就是只能读不能写的存储器,但现在的 ROM,基本都是可读可写的,只是速度比 RAM 慢而已。

实际上,早期的 ROM 设备确实是只能读,后来随着市场需求的改变,才诞生了可读可写的 ROM,并且 ROM 也不是一下子就可以写了,而是慢慢发展成目前的样子的。

按照书上的介绍,ROM 具体分为以下几种:

- 掩膜 ROM(MROM):行列选择线交叉处有 MOS 管为 1,无 MOS 管则为 0

- PROM(一次性编程):以行、列线间的熔丝是否熔断区分 1 和 0,熔断为 0,反之为 0

- EPROM(多次性编程)

- EEPROM(也叫 $E^2PROM$,多次性编程):电可擦写,支持局部擦写和全部擦写

- Flash Memory(闪速型存储器,也叫闪存):读写速度很快、功耗低,但价格较高

存储器与 CPU 的连接

这一块内容算是重点与难点内容了🤐。

存储器容量的扩展

首先是存储器容量的扩展,主要是三种方式:位扩展、字扩展和字位扩展。

位扩展

位扩展其实就是增加存储字长,比如用 2 片 $1K \times 4$ 位存储芯片组成 $1K \times 8$ 位存储芯片,就只是把存储字长扩大了一倍。但不论是 2 片 $1K \times 4$ 位存储芯片还是 1 片 $1K \times 8$ 位存储芯片,总体的存储容量都是 $8K$ 位(这个说法可能不严谨,懂意思即可)。

字扩展

字扩展就是增加存储字的数量,比如用 2 片 $1K \times 8$ 位存储芯片组成 $2K \times 8$ 位存储芯片,本质上相当于是把存储单元的数目扩大了一倍。但不论是 2 片 $1K \times 8$ 位存储芯片还是 1 片$2K \times 8$ 位存储芯片,总体的存储容量都是 $16K$ 位。

字、位扩展

字、位扩展就是字扩展与位扩展结合使用的方式,比如用 8 片 $1K \times 4$ 位存储芯片组成 $4K \times 8$ 位存储芯片。

与 CPU 的连接

存储器与 CPU 的连接主要包括六个部分:

- 地址线的连接

- 数据线的连接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他芯片或控制电路,如时序、负载

以书上的例题 4.1 和 4.2 作为例子,老师讲的很清楚,书上写的也很清楚,这里不再赘述了,只记录下主要的解题步骤是:

- 写出相应的二进制地址码

- 确定芯片的数量及类型

- 分配地址线

- 确定片选信号

存储器的校验

存储器的校验是通过一系列的编码方法来完成的,这一章主要介绍汉明码。

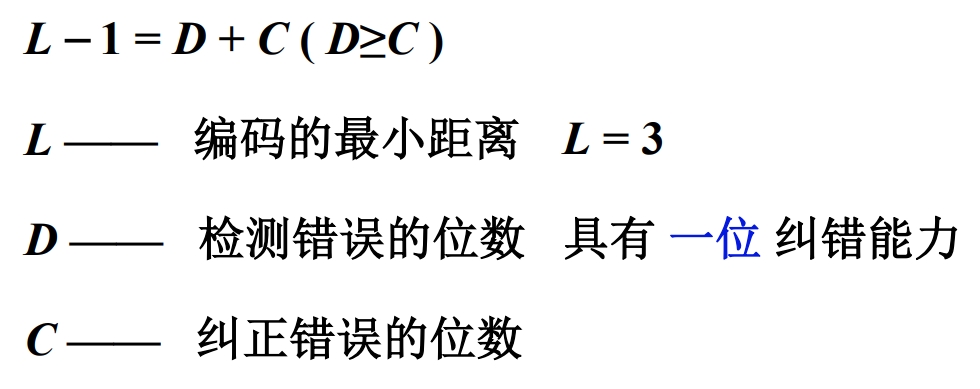

首先要明确汉明码中码距的概念,也即两个合法代码对应位上编码不同的位数称为码距。编码的纠错、检错能力与编码的最小距离有关,而汉明码是具有一位纠错能力的编码。

需要注意以下汉明码组成的三要素,如下图:

汉明码的配置、检错过程,这里就不再赘述了,老师讲解的很清晰,书上也解释很清楚。

提高访存速度的措施

按照老师的讲解,提高访存速度的思路就是三个方面:

- 采用高速器件

- 采用层次结构,比如 Cache-主存

- 调整主存结构

前两点已经在前面提到过了,这里在提一下第三个思路,主要有两个方式:

- 单体多字系统,本质是增加存储器带宽

- 多体并行系统,分为两种方式:高位交叉、顺序编址(各个体并行工作)和低位交叉、各个体轮流编址(在不改变存取周期的前提下,增加存储器的带宽)。

最后的内容就是几种高性能存储芯片:

- SDRAM(同步 DRAM),在系统时钟的控制下进行读出和写入,CPU 无须等待,也就是现代计算机的内存条

- RDRAM,由 Rambus 开发,主要解决存储器带宽问题

- 带 Cache 的 DRAM,在 DRAM 的芯片内集成了一个由 SRAM 组成的 Cache,有利于猝发式读取

总结

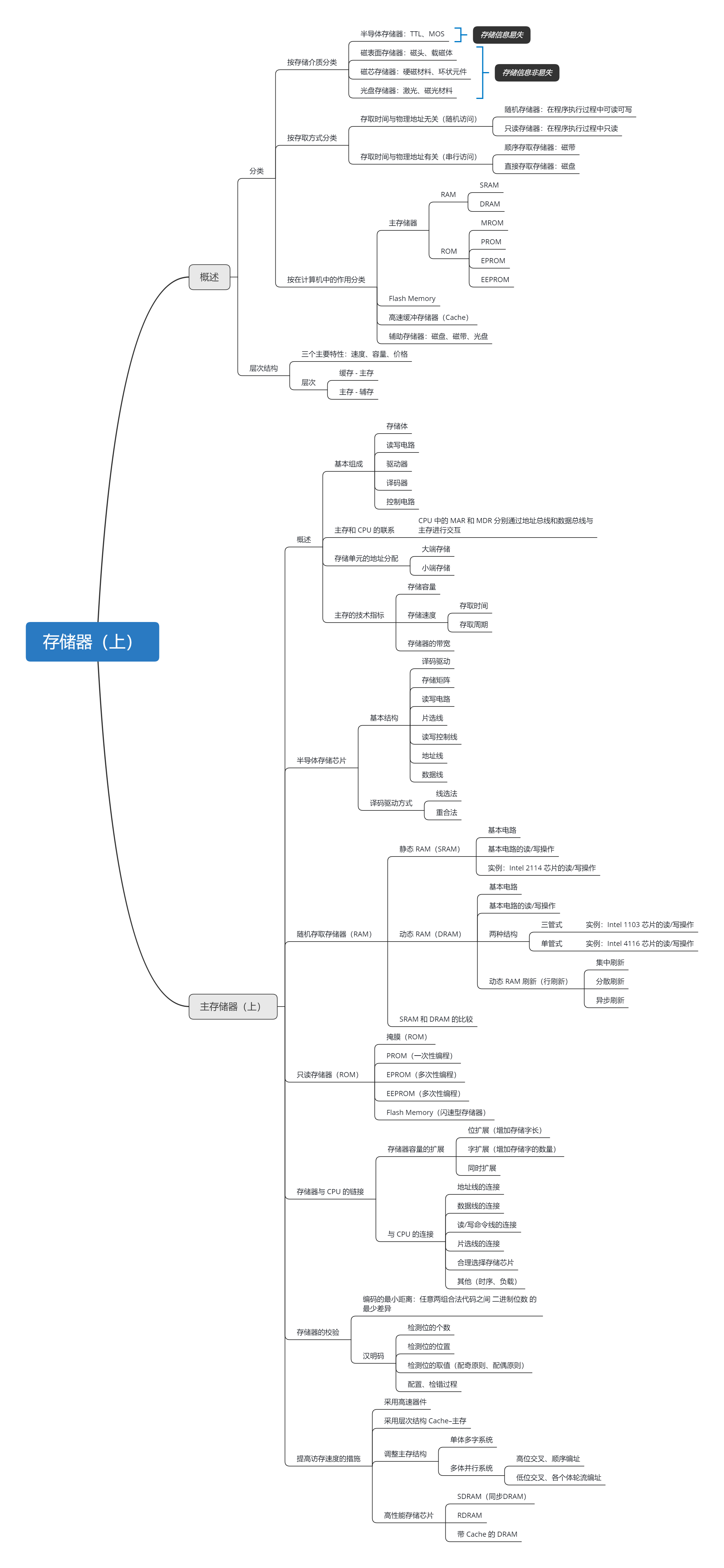

在上周基础上添加本周内容后的思维导图:

本周的重点内容在存储器与 CPU 的连接部分,从应试的角度来讲,这块内容应该很容易出综合大题,因为这里可以把 CPU 和总线的内容结合起来,所以最好把书上的几个例题吃透。还有一个考点,应该是汉明码,这块知识点,要是不理解,做题估计还是错,建议找题目做做看。

好消息是,我不用考试了,只要理解大部分知识点就可以了😂。