这周存储器,不知道会不会有趣一点...😴

听完了,才知道也不是很有趣...😂

有关存储器的内容一共分了三周的课程,这周的主要内容是有关主存储器的部分。

存储器

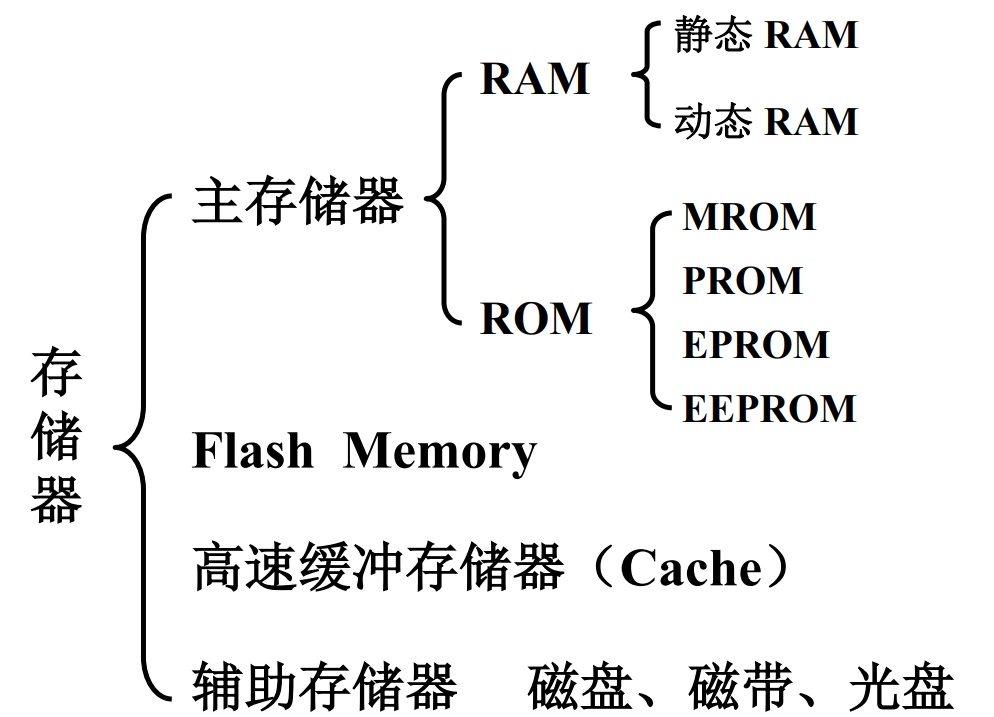

首先要介绍的是存储器的分类和现代存储器的层次结构。

分类

1. 按照存储介质分类

- 半导体存储器

- 磁表面存储器

- 磁芯存储器

- 光盘存储器

注意:半导体存储器存储的信息是易失的,而其他三种存储器是非易失的。

2. 按照存取方式分类

- 当存取时间与物理地址无关(随机访问),可分为随机存储器(在程序的执行过程可读可写)和只读存储器(在程序的执行过程中只读)。

- 当存取时间与物理地址有关(串行访问),可分为顺序存取存储器(如磁带)和直接存取存储器(磁盘)

3. 按在计算机中的作用分类

层次结构

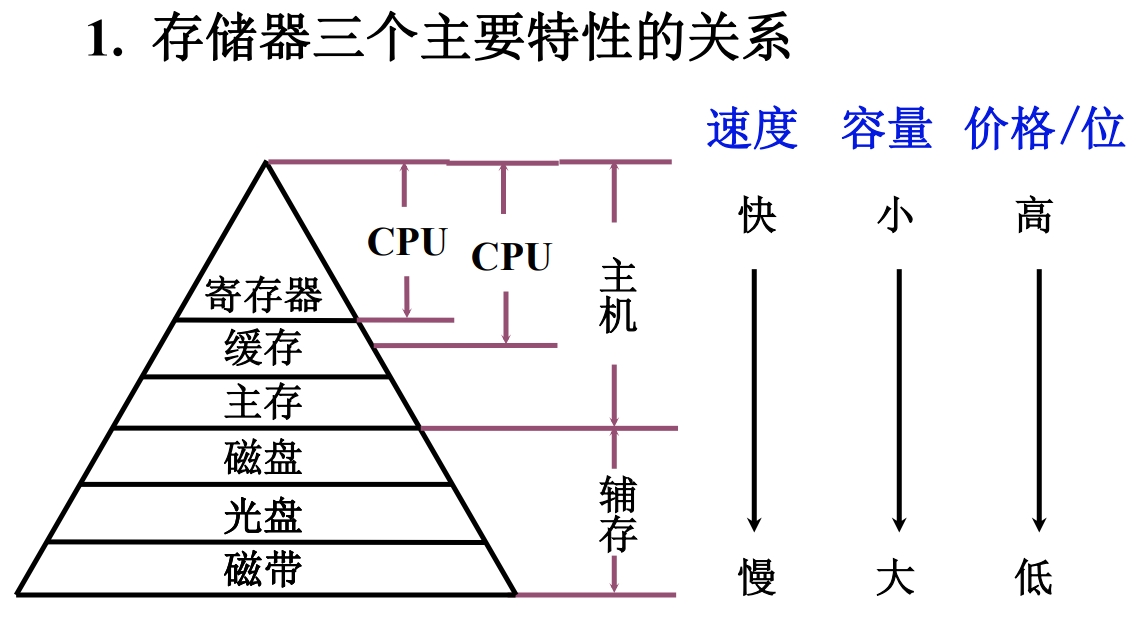

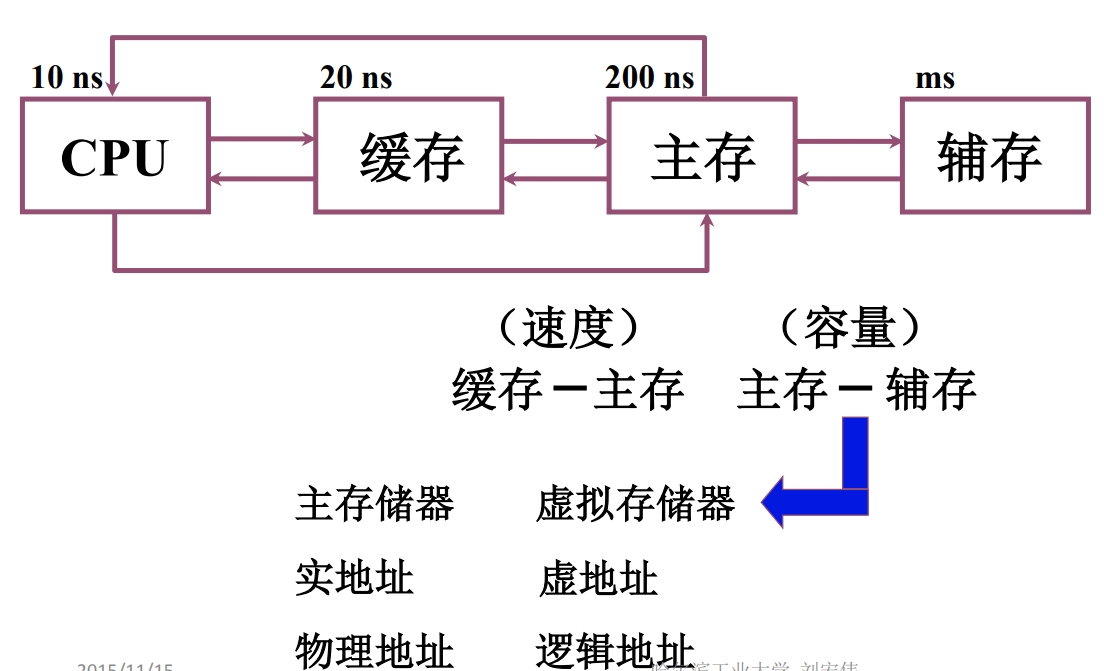

不多说了,主要看下面两张图:

上面这张图主要是在说明:越贴近 CPU 的存储介质的速度越快、容量越小、价格越贵,所以如何把计算机的结构设计的经济合理就是一个很重要的问题了。

这张图实际上就是上述问题的答案,对于用户体验而言,并不需要每一块存储芯片都有很快的读写速度(对用户而言,性价比才是王道,哈哈~),而且从功能上而言,速度依次递减也不会对整个计算机构成影响。

主存储器

第一张提到的有关存储器的知识这里依然用得到,之前是大概了解,现在是深入了解。

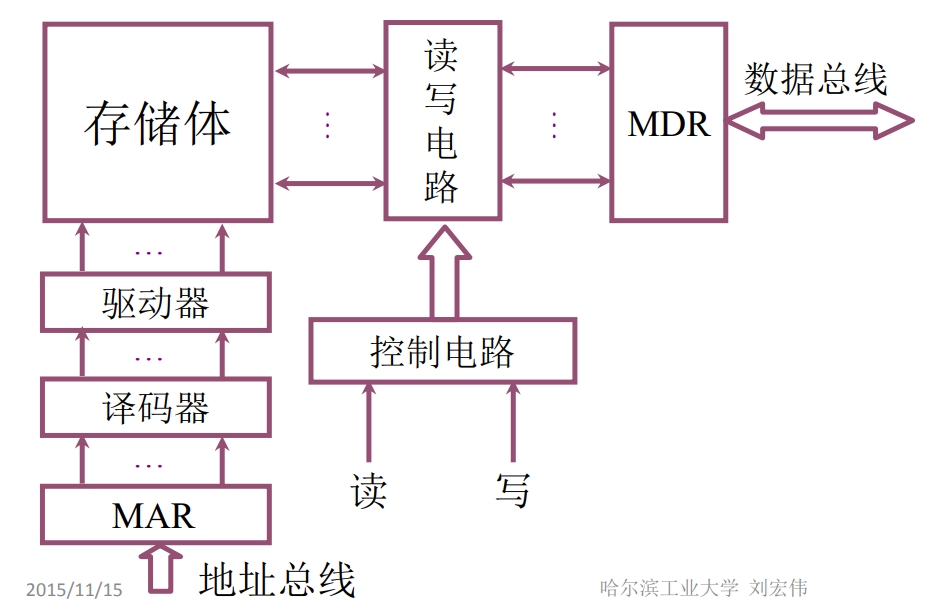

概述

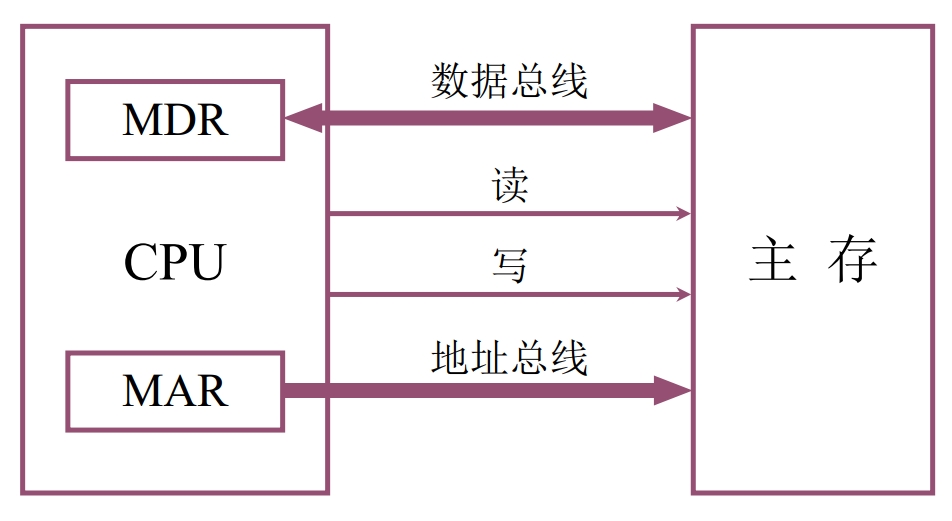

首先要了解的是主存储器的基本组成,见下图(还是电路之类的东西):

对应的是,CPU 和主存的联系,见下图:

这里又提到了大端存储和小端存储的概念:

大端存储:数据的高字节保存在内存的低地址中,而数据的低字节保存在内存的高地址中。

小段模式:数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中。

举个简单的例子,0x12345678,如果是大端模式,对应内存中保存的值就是12 34 56 78;如果是小端模式,对应内存中保存的值就是78 56 34 12。

最后是主存的技术指标,主要是是存储容量、存取速度、存储带宽(位/秒)这些概念。

存取速度相关的概念有两个:

- 存取时间:存储器的访问时间,可分为读出时间和写入时间。

- 存取周期:连续两次独立的存储器操作(读或写)所需的最小间隔时间,可分为读周期和写周期。

半导体存储芯片

首先要学习的是半导体存储芯片的相关知识,主要分两块:基本结构和译码驱动方式。

基本结构

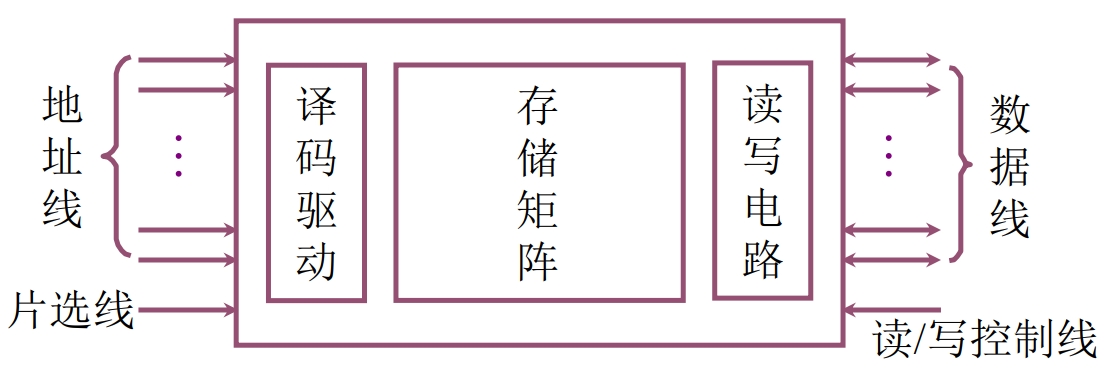

半导体存储芯片的基本结构见下图:

相比前面介绍的主存的基本组成,多了片选线(确定那块存储芯片被选中)和读写控制线(确定芯片进行读/写操作)。实际上,个人认为这两部分组合在一起就是存储器的“控制器”,由它来决定存储器的一些行为。

另外,片选线中存在两个信号:$\overline {CE}$ 和 $\overline {CS}$;读/写控制线中存在三个信号:$\overline {WE}$(低电平写,高电平读)、$\overline {OE}$(允许读)和 $\overline {OE}$(允许写)。

关于片选信号的作用,老师举了一个例子:组成一个$64K \times 8$位的存储芯片需要使用 4 组$16K \times 1$位的存储芯片,且每组 8 个,一共 64 个,此时由两个片选信号就可以唯一确定是对那一块$16K \times 1$的芯片进行操作,实际上这个过程类似于通过矩阵的行列坐标来确定其中的特定元素。

译码驱动

半导体芯片的译码驱动方式这里介绍了两种:线选法和重合法。

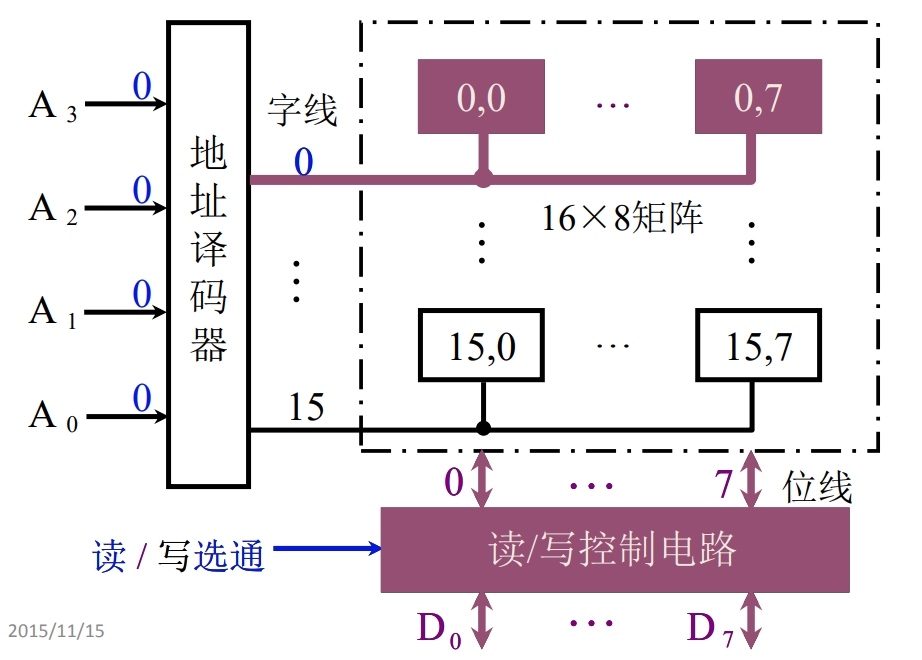

线选法

如下图所示:

$A_0 - A_3$作为地址码会被地址译码器解析为对应的字线,4 个 bit 正好对应 16 根线,还有 8 根位线连接在读/写控制电路上。

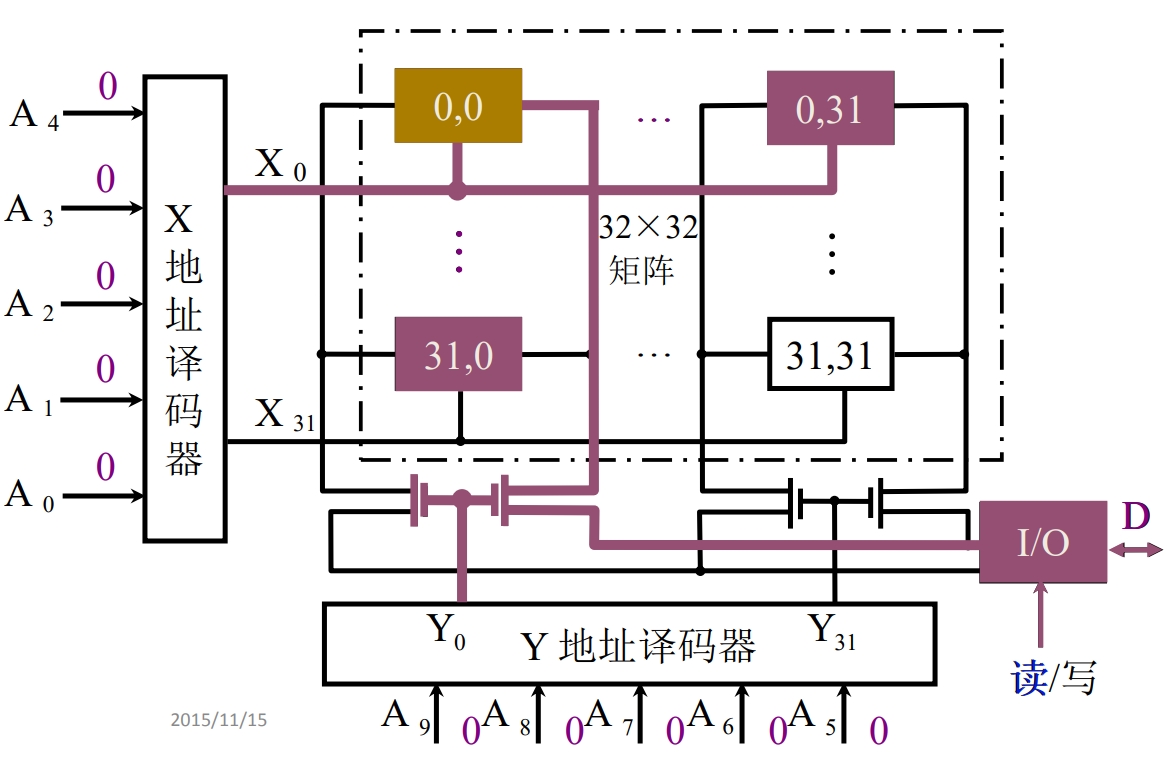

重合法

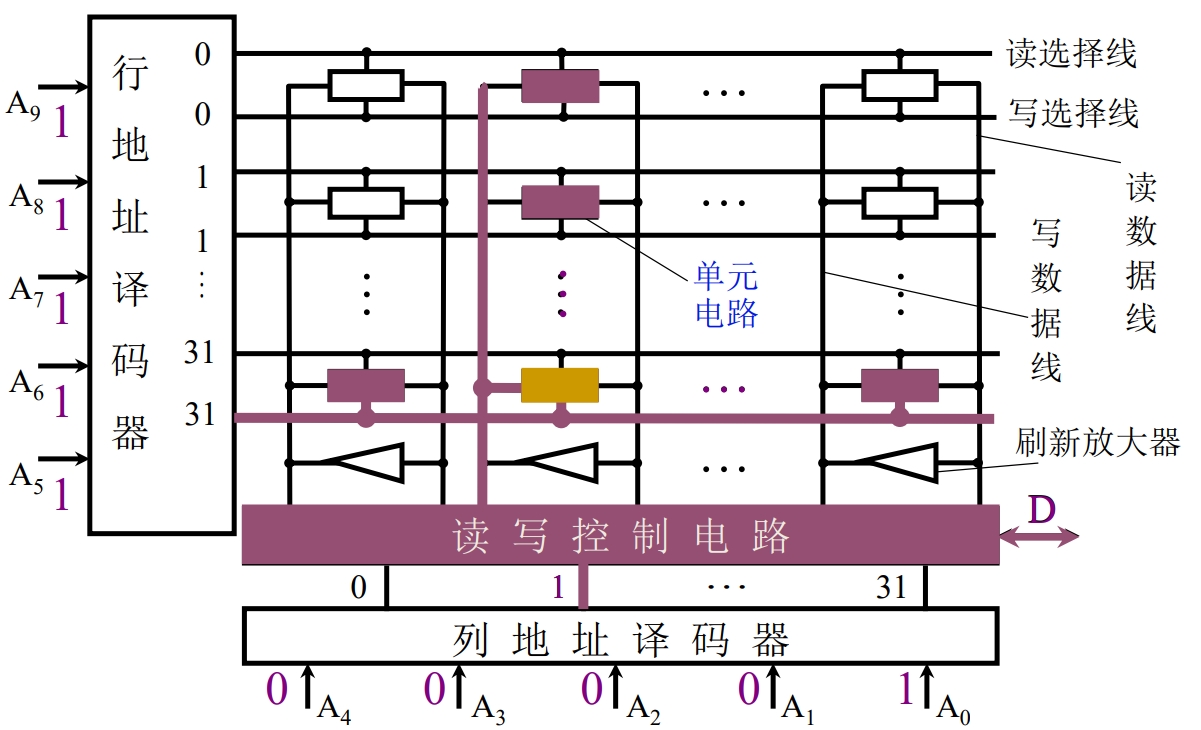

如下图所示:

重合法感觉要简单一点,$A_0 - A_4$作为 X 地址码,5 个 bit 位对应 32 根线,$A_5 - A_9$作为 Y 地址码,也是 5 个 bit 位,对应 32 根线,X、Y 实际上就可以当作是横纵坐标了。

RAM

随机存取存储器(RAM)分为两种:静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)。

SRAM

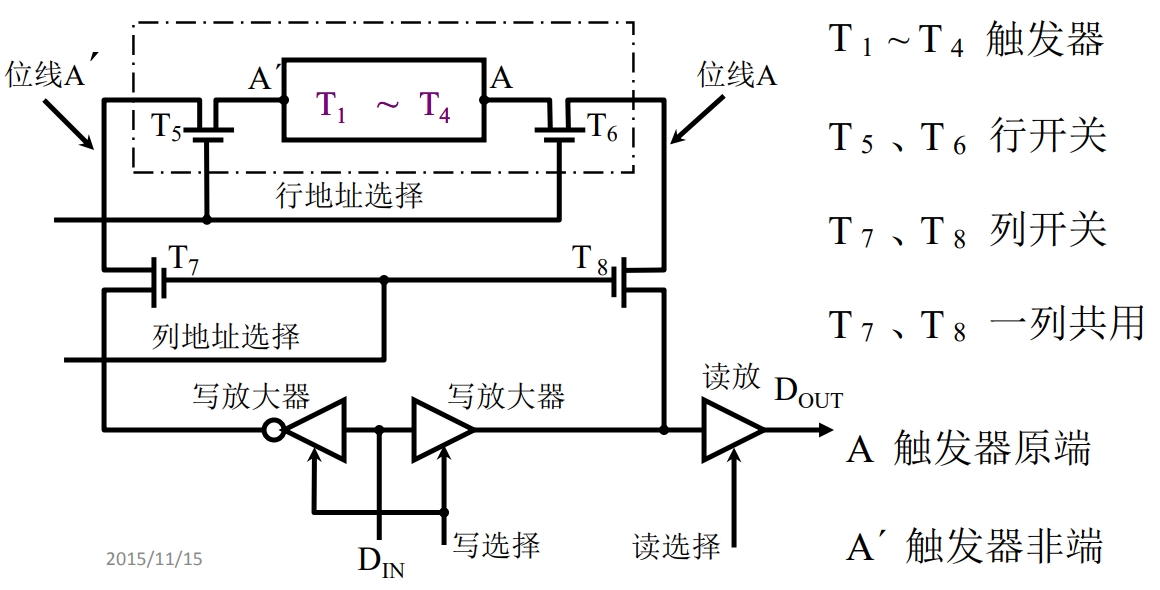

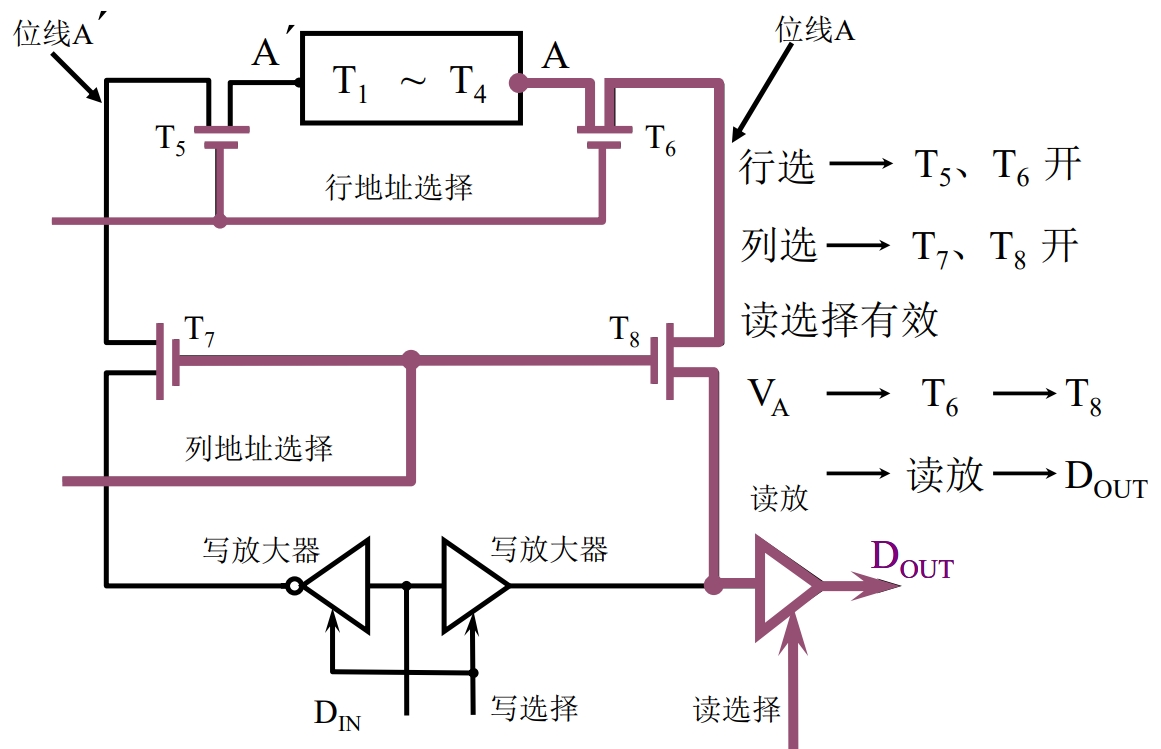

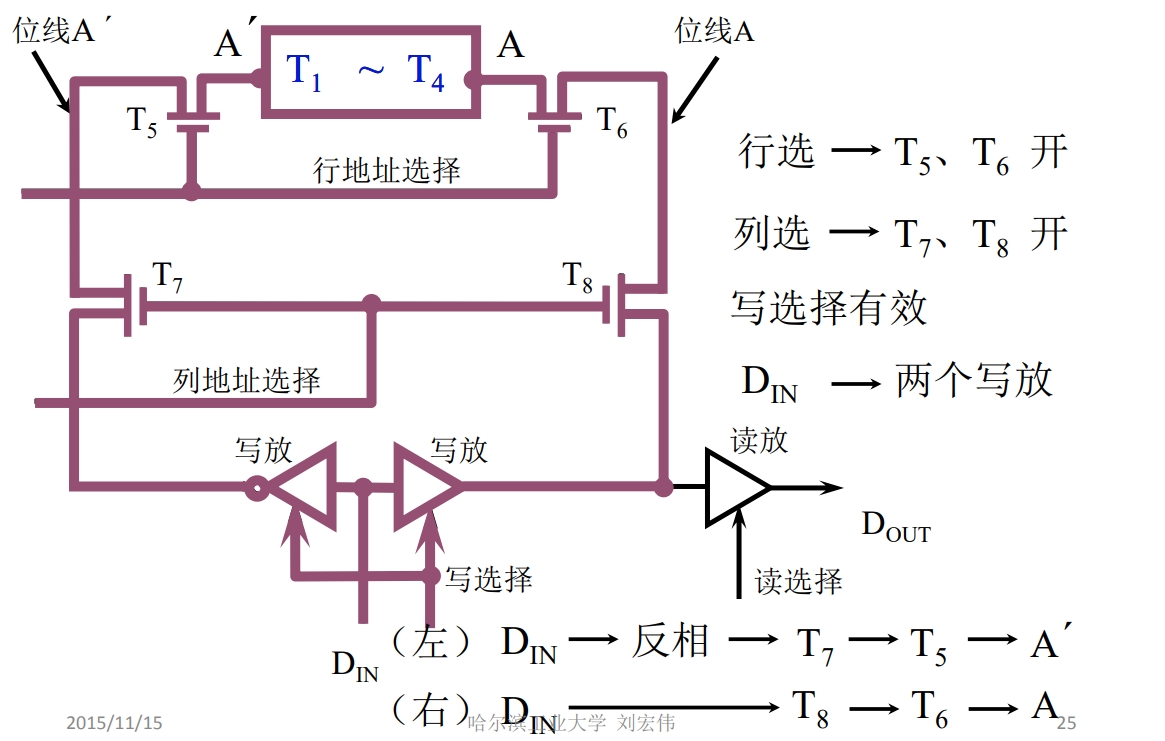

静态随机存取存储器是由双稳态触发器组成,断电后会丢失信息,存取速度快,基本电路如下:

这里不深究电路的设计思路和原理了...🤐

读操作:

写操作:

最后提到了一个实际用重合法组成的芯片——Intel 2114,本质上是一个$64 \times 64$的矩阵,这里不做深究了。

DRAM

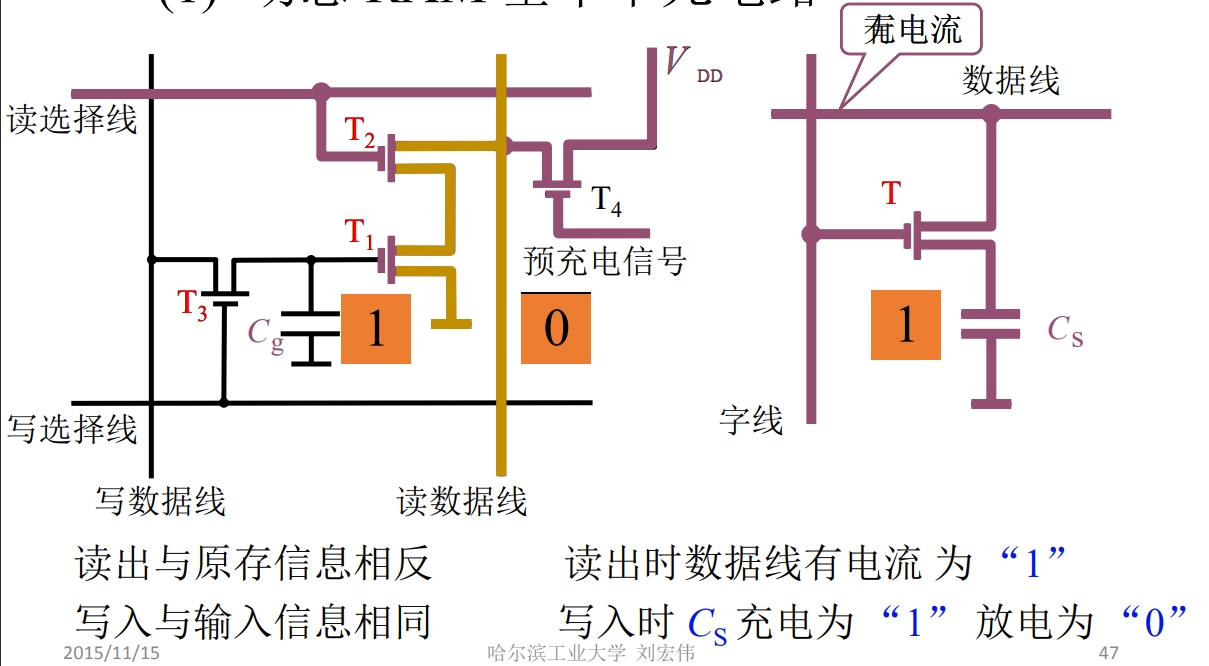

动态随机存取存储器是由电容组成,同样断电后会丢失信息,速度比 SRAM 慢,基本电路如下:

在上图中,左边是三管式存储电路,右边是单管式存储电路。

三管动态 RAM 芯片的读写操作过程是类似的,这里简单分析一下 Intel 1103 芯片的写操作,如下图:

实际上就是下面两个要点:

- 与重合法类似,三管动态 RAM 芯片的译码过程也是需要分别使用行列地址译码器来完成,不同的地方在于三管式区分开了读/写选择线,所以行地址译码的过程实际上有读写控制电路的参与。

- 每一列都需要有一个刷新放大器来形成再生信息,原因是电容会漏电(老师的原话😐)。

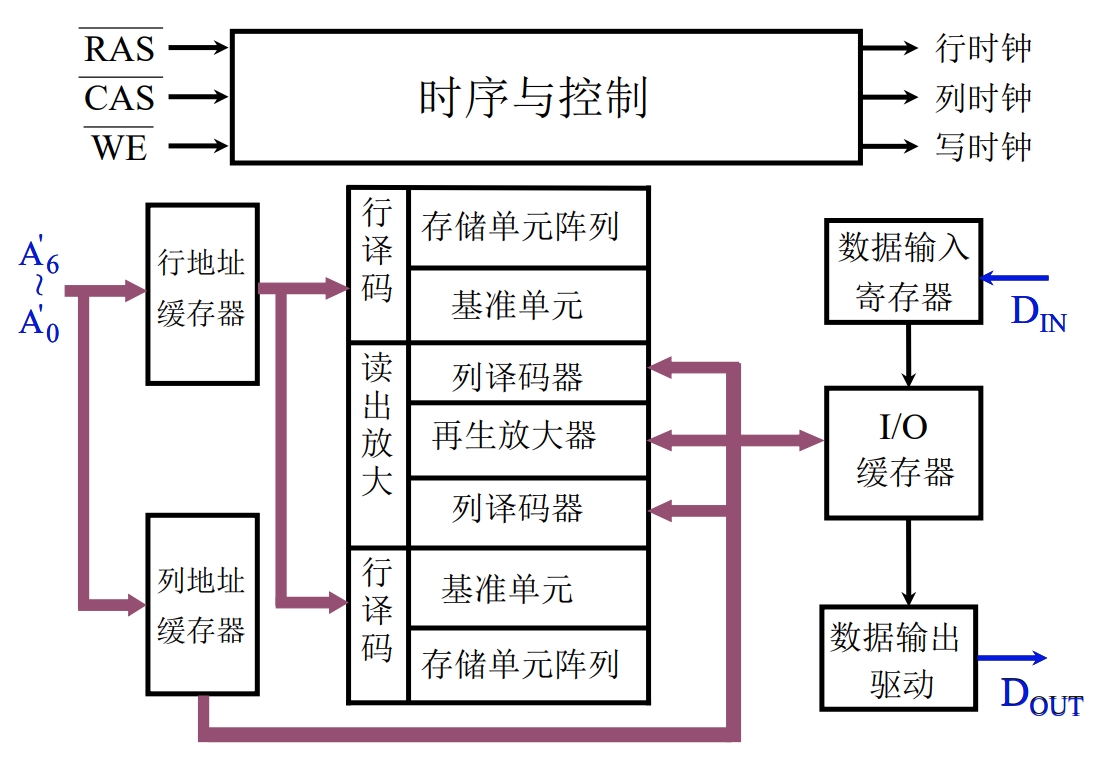

然后是单管动态 RAM 芯片,这里以 Intel 4116 芯片为例,首先是 Intel 4116 的外特性,如下图:

这个结构有两个要点:

- 整个芯片只有 7 位地址线,输入的行列地址会先存放在行列地址缓存器中,然后在进行后续的译码过程。

- 这个芯片内部还有一个小控制器:时序与控制控制器,这个控制器利用行选中信号($\overline {RAS}$)、列选中信号($\overline {CAS}$)和读写控制信号($\overline {WE}$)作为输入,产生行时钟、列时钟和写时钟,来控制芯片内部的读写操作。

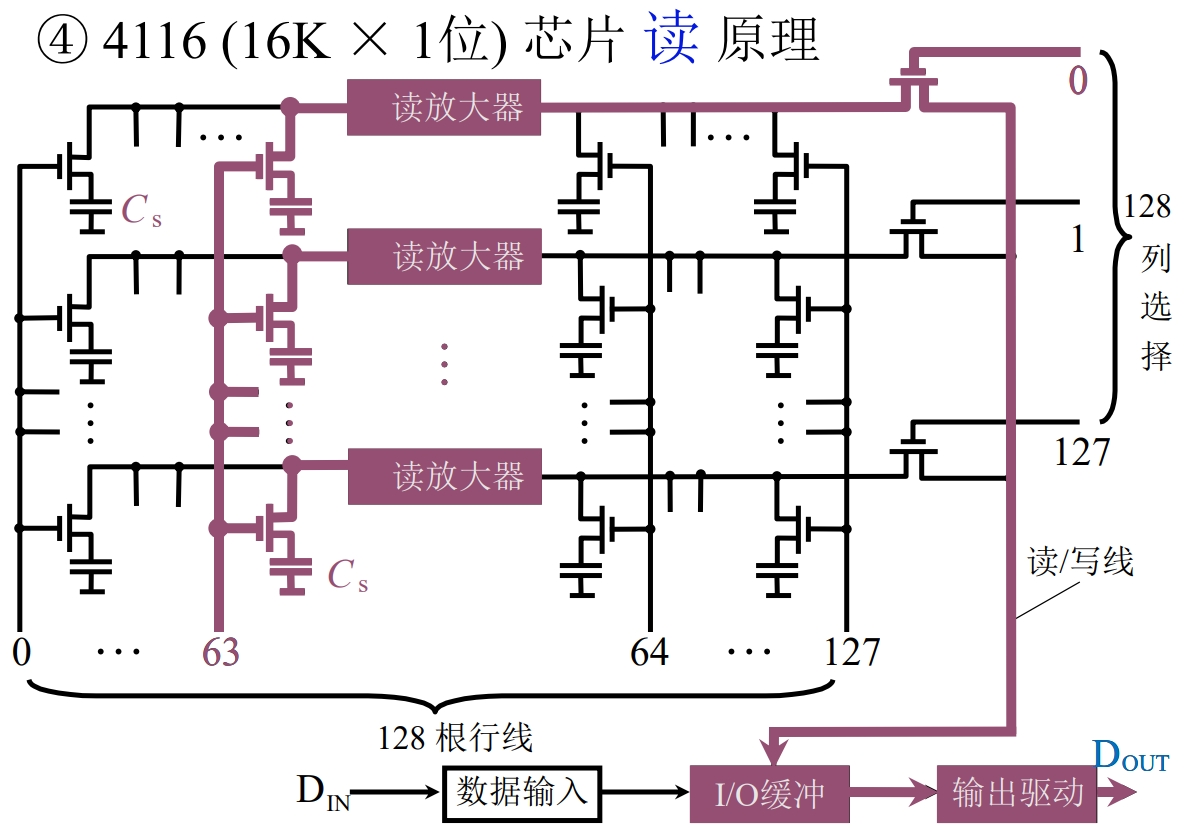

Intel 4116 的读/写操作也是类似的,这里以读操作为例,如下图:

同样,Intel 4116 也需要放大器来形成再生信息,同时这个放大器两端产生的信号是相反的。而寻找存储单元的思路依然是重合法那一套,行列信号当作坐标即可。

DRAM 最后一个问题是关于刷新的问题,也就是上面提到的因电容漏电而需要放大器形成再生信息。刷新的整个过程是针对一行而言,对应的刷新方法有三种:集中刷新、分散刷新和异步刷新(二者结合)。

集中刷新

集中刷新其实就是集中一个时间段进行刷新,以 $128 \times 128$ 矩阵为例,需要 128 个周期进行刷新,假设芯片的存取周期是 $0.5\mu s$,刷新时间间隔是 $2 ms$,所以刷新时间就是 $0.5 \mu s \times 128 = 64 \mu s$,在这个时间段中,CPU 与 I/O 都无法与 DRAM 交互,故这个时间段也叫“死区”,对应的“死时间率”为 $128 / 4000 \times 100\% = 3.2\%$ 。

分散刷新

分散刷新是在每一个存取周期进行刷新,也就是读写操作完成后直接进行刷新。以上面提到的例子为例,在分散刷新的条件下,整个存取周期就从 $0.5 \mu s$ 变成了 $1 \mu s$,这种方法虽然消除了“死区”,但 DRAM 根本不需要这么频繁的刷新。

异步刷新

所谓异步刷新,其实就是集中刷新和分散刷新结合。还是上面的例子,若每 $15.6 \mu s$ 刷新一行,只需要把这一次刷新操作安排在最后集中刷新即可,这样对整个刷新时间间隔就是分散刷新了。同样,由集中刷新带来的“死区”是 $0.5 \mu s$,但如果将刷新安排在指令译码阶段,就不会产生“死区”了。

SRAM 和 DRAM 的比较

SRAM 一般用来做 CPU 的缓存(Cache),DRAM 一般用来做主存(RAM),二者差别见下表:

| 类别 | DRAM | SRAM |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

总结

这周的内容依然是偏理论性质的,实在是谈不上有趣,只能耐着性子听下去😂。总体听下来,出现了很多和电路相关的术语,不得不说,与《组成原理》结合紧密的课程还得是《数字电路》。不过,单从原理的角度来讲,倒也可以用死记硬背来解决。

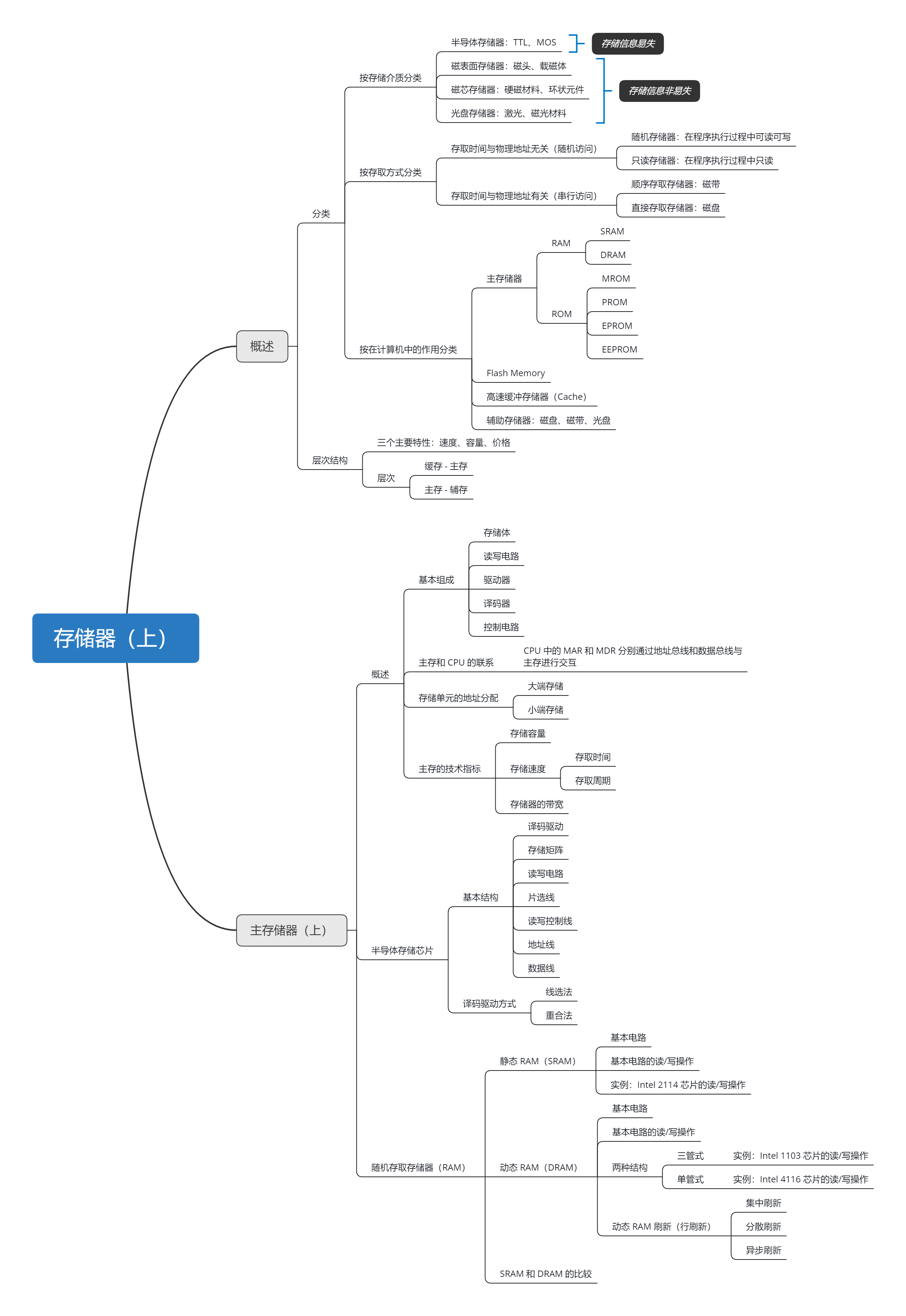

好了,这周的内容的思维导图如下:

剩下的事情就是把题目解决了...😴